本系列文章为《High Speed Serdes Devices and Applications》的学习总结,素材主要取自教材,并附带一些自己的思考。原书下载链接:High Speed Serdes Devices and Applications.pdf

PLL(Phase-Locked Loop,锁相环)

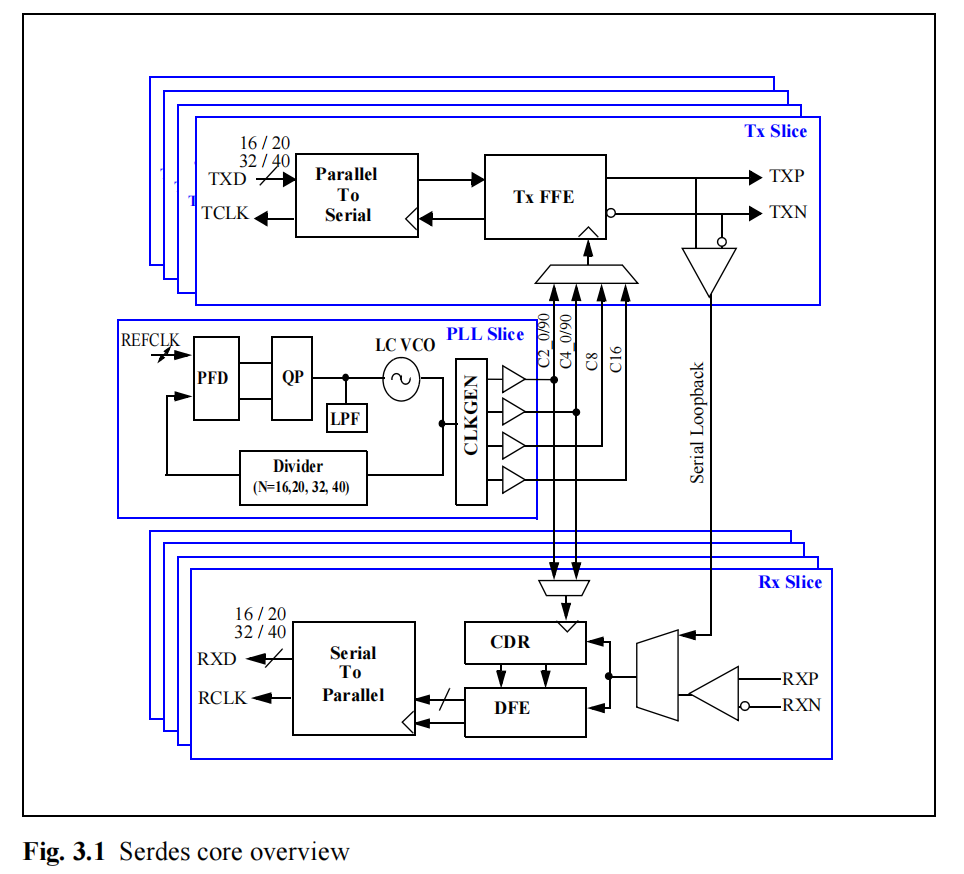

如果要粗略的分割Serdes的结构,那么通常可以说Serdes Core 由 Tx 、Rx 以及PLL三个子模块组成,如图3.1所示。本文将详细介绍PLL的实现原理和内部结构,帮助读者理解。

PLL的用途:

1)well-defined clock ——需要有明确定义的时钟供系统或者模块使用,用于同步。

2)分频或者倍频时钟,可以在系统内部进行时分复用。

3)Frequency Synthesizer 频率合成器,在多载波系统中快速跳频,例如蓝牙,WiFi通信中切换channel。只有PLL能够做到低相邻载波干扰。

4)CDR(clock data recover)时钟恢复。这个也是serdes里面重要应用。

5)频率调制,例如FM,FSK,QAM,OFDM等等。

6)SSC(Spread Spectrum Clocking,扩频时钟),串行协议中的时钟频率偏移,用于降低电磁干扰(EMI,Electromagnetic Interference)。

通过输入一个参考时钟,PLL可以输出你想要的时钟。

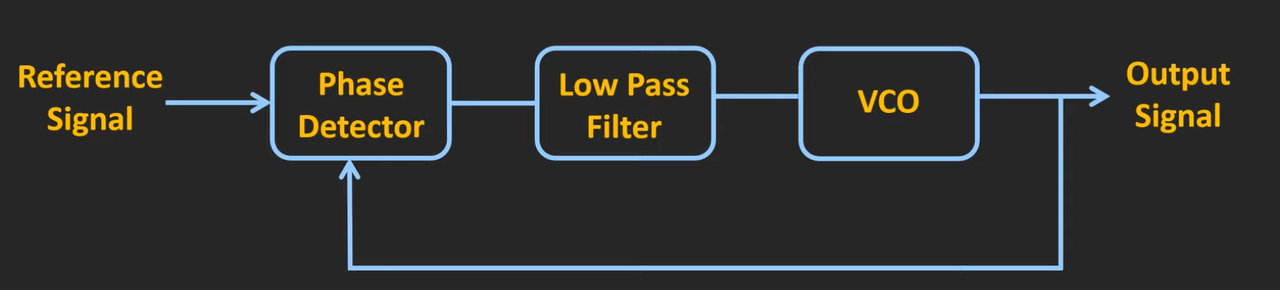

最简单的PLL结构,Simple PLL

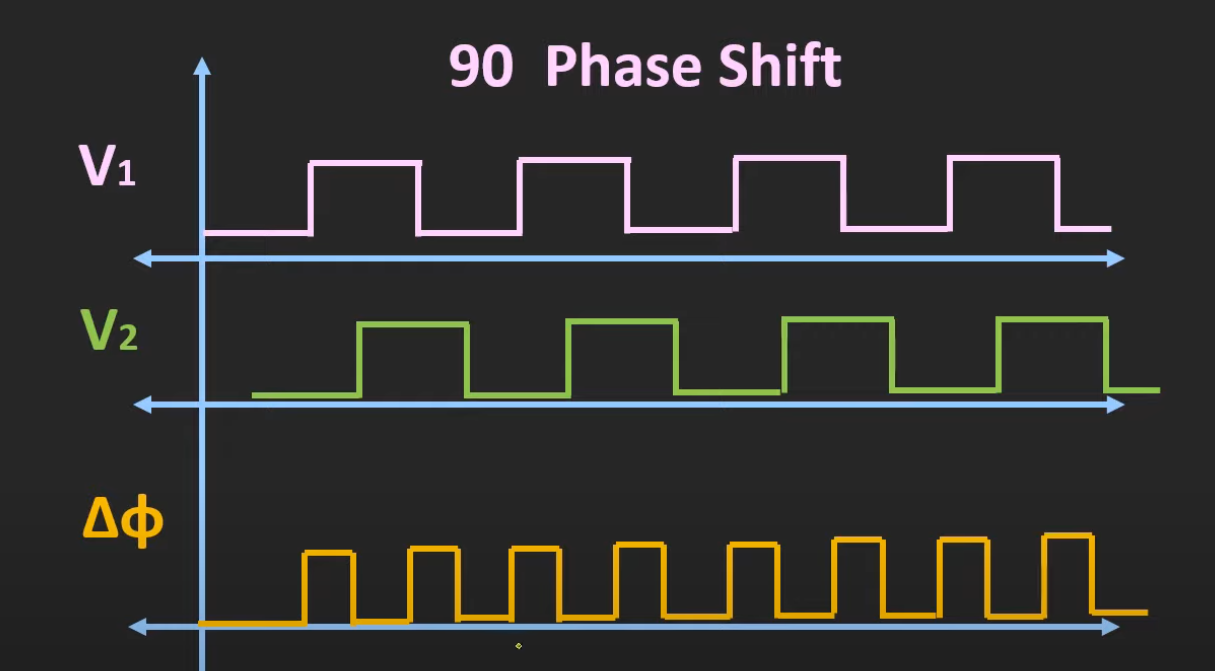

假设有一个异或门,两个输入为V1,V2,输出为Vo:

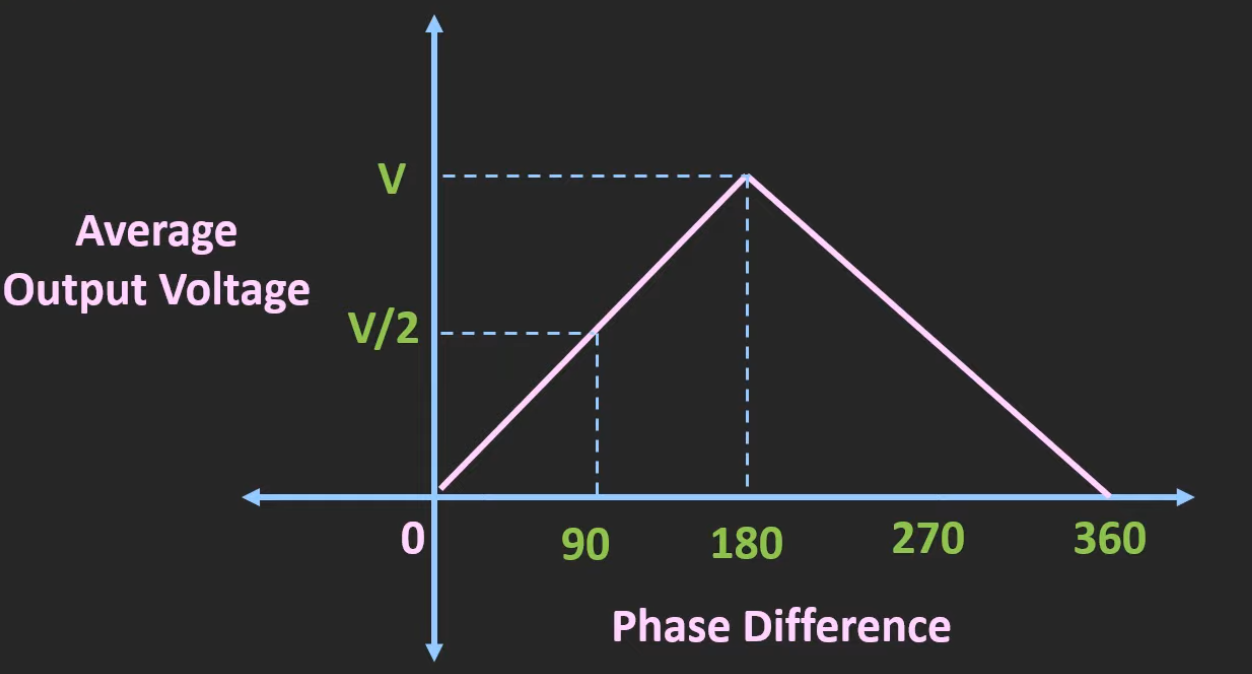

他们之间的相位关系如上图所示,让输出Vo经过一个低通滤波器,那么滤波后的电压可以看成平均值,这个平均电压和V1、V2之间的相位差是线性关系,如下图所示:

由这个输出电压来控制VCO(压控震荡器):

压控振荡器的输出频率和电压的关系可以看成:

是自由震荡频率,是VCO没有电压输入时的频率。或者可以写为:

其中 为自由振荡角频率, 为 VCO 增益。

相位检测器(PD)将相位误差 转换为电压信号 ,其输出通常为 :

其中 为相位检测器增益。

设低通滤波器的响应函数为,则在拉普拉斯域中。

VCO 的输出相位变化率为:

取拉普拉斯变换,假设初始条件为零,得到:

因此:

闭环关系

将 代入 VCO 方程代入:

得到:

移项整理:

提取:

闭环传递函数 :

因此:

稳态分析

在锁相状态下, 需跟踪 ,反馈调整使 的稳态影响趋于零(通过 补偿)。

假设输入为纯相位信号(无 项),则:

这里如何理解?

稳态时,后面一项可以忽略,这里的含义是,达到稳定状态之后,VCO的输出频率就和无关,只受到输入频率 的影响。或者说,我们这里的分析考虑的是小信号建模, 实际上会将这个自由频率带来的影响减去。

如果代入一阶低通滤波器的传递函数:

得到:

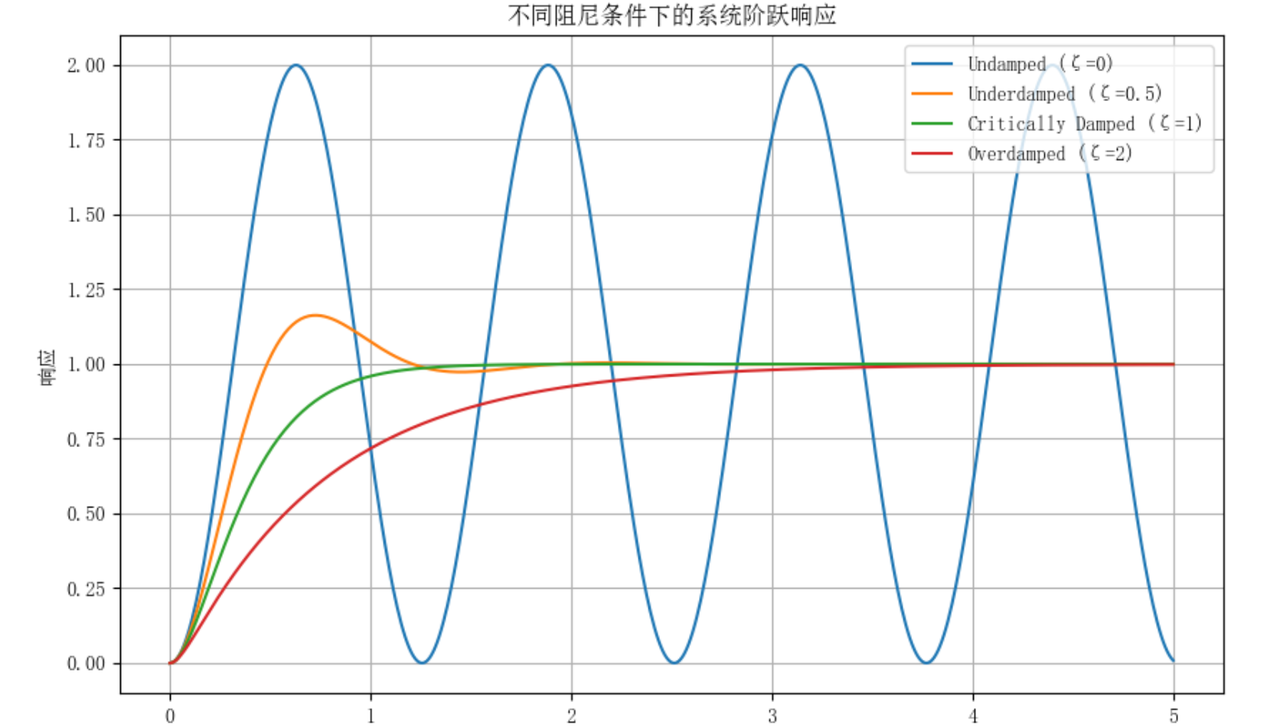

这就说明整个PLL的传递函数可以看成是一个二阶的低通滤波器。也就是说,如果输入信号频率(相位)突变,输出会缓慢跟随直至相等。具体是怎么恢复到稳态,与低通滤波器和VCO,PD属性有关,即过阻尼,欠阻尼,临界阻尼三种跟随方式。

图中通过欠阻尼 (ζ<1 ) 和过阻尼 (ζ>1 ) 的响应曲线,揭示了 PLL 设计中的动态性能与稳定性的矛盾,总结如下:

欠阻尼 (ζ<1 ):

特性:响应曲线显示振荡("Wants rings to settle"),即输出 在跟踪时出现过冲和振荡,最终收敛。

问题:振荡可能导致相位噪声或频率不稳定,尤其在高速跳频(如 RF/Wireless/mmWave 应用)中,影响信号质量。

应用场景:适合需要快速响应的场景,但牺牲了稳定性。

过阻尼 (ζ>1 ):

特性:响应曲线平滑上升("Wants settle"),无振荡,但收敛较慢。

问题:缓慢的上升时间可能无法满足快速通道切换的需求,尤其在无线通信中要求快速频率调整。

应用场景:适合需要稳定性的场景,但牺牲了响应速度。

总结异或门 + 低通滤波器的具体问题

异或门作为相位检测器:

异或门输出与相位差 成线性关系,但其增益 较低,且对大相位误差(> π )非线性,限制了锁相范围。

低增益导致 较小,环路带宽窄,动态响应较慢。

低通滤波器 (LPF):

LPF 滤除高频噪声,但若截止频率设计不当(太低),会进一步减慢响应;若太高,则无法有效抑制振荡。

这也说明了这种结构的Simple PLL存在着以下问题:

稳定时间和抖动之间的矛盾。

Phase 之间的关系不确定,随着温度电路改变。

存在稳定性问题,即欠阻尼下过冲震荡。

不知道锁定范围有多大,与回路带宽有关。

——————————————————————————————————————————

参考链接:李致毅教授 B站视频:鳌中堂讲电路

图片部分来源:What is Phase Lock Loop (PLL)? How Phase Lock Loop Works ? PLL Explained

Serdes 学习笔记,锁相环(PLL)结构和原理(其一,Simple PLL)

https://blog.songshiyu.cn/archives/serdes-xue-xi-bi-ji-plljie-gou-he-yuan-li-qi-yi-simple-pll

评论