本系列文章为《High Speed Serdes Devices and Applications》的学习总结,素材取自教材,并附带一些自己的思考。原书下载链接:High Speed Serdes Devices and Applications.pdf

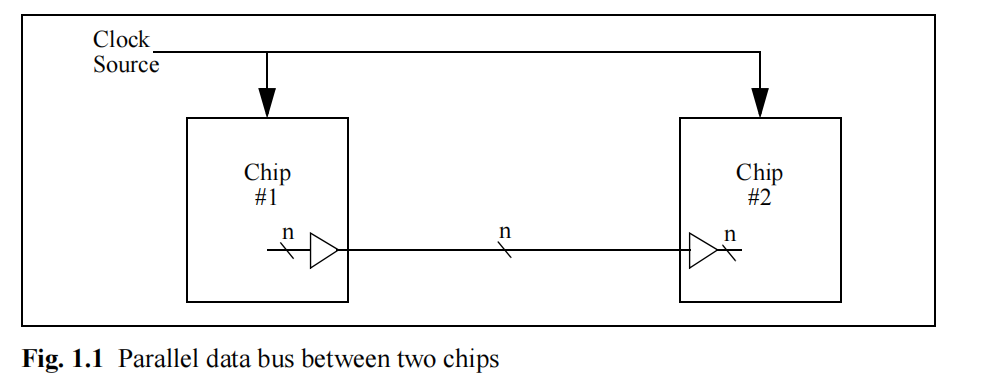

传输数据最简单的方式就是直接将不同芯片(Chip)的输入输出直接连接起来,为了提高传输速率,可以采用并行接口(Parallel Interface),由于两个芯片是使用的同一个时钟源,因此可以看成同步电路直接传输,如图1.1所示。

但是随着集成电路的发展,对数据传输的要求越来越高,这种方式存在以下几个问题:

1)芯片内部晶体管集成度越来越高,电路越来越复杂,因此数据交换速率提升,但是芯片封装水平没有得到同样的发展,IO管脚的数量与数据传输量不匹配。

2)数据传输时序控制过于复杂,Chip1和Chip2之间的数据能够正确传递是因为使用了同一个时钟源,数据传递到Chip2时,Clock需要满足保持/建立时间,但是数据bit之间的传输延迟不一定相同,数据bit和时钟clock之间的传输时延不相同,这就导致要满足所有bit位的采样时间在高频时钟下变得异常困难。

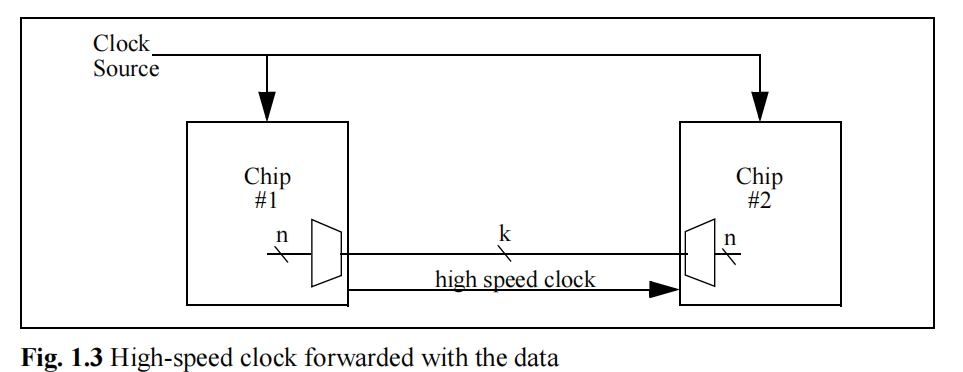

为了解决这个问题,可以使用源同步架构,并且通过串行化的方式减少IO管脚。如图1.3所示。

对比图1.1,这种架构有以下不同:

1)IO管脚由n变成了k,数据发送前先经过Chip1的Mux选择复用,然后在Chip2中解复用还原成n bit。

2)除了数据,还有一个高速时钟一起传输给Chip2,该时钟是Chip1的数据发送时钟,也是Chip2的数据采样时钟。

这样做的好处是,Chip1发送的时钟也给Chip2作为参考时钟,我们不用考虑Chip1和Chip2的时钟网络带来的延迟的影响,因为这里用的都是Chip1的时钟,只需要关注时钟和数据之间的走线延迟的差异。一般而言,在这中情况下,数据和时钟的走线延迟在一定程度上是相关的,这给时序分析带来的便捷,裕量需要那么高。

需要注意的是,Chip2只是在采样的时候使用了high speed clock时钟,其他逻辑仍然使用的是Clock Source 经过PLL倍频得到的时钟,因为这个时钟性能更好,更加稳定。而非所有地方都是用这个传递过来的高速时钟。例如 数据经过high speed clock采样后进入一个FIFO,FIFO的读时钟是由Clock Source 的倍频时钟,这个时钟和高速时钟频率相同,但是相位不同。

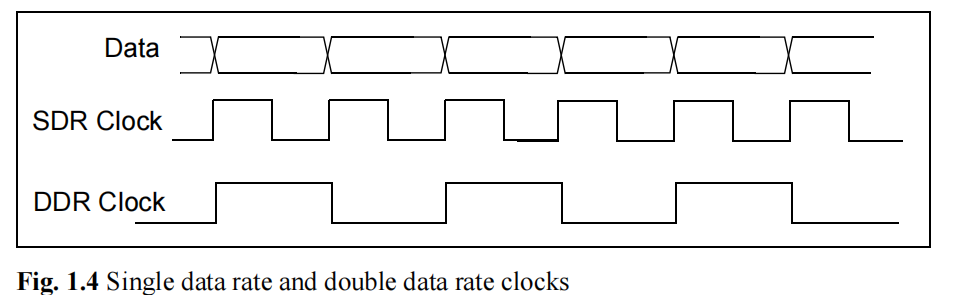

高速时钟和数据可以是SDR,也可以是DDR,SDR是指仅在上升沿或者下降沿采样,DDR是双边沿采样。如果使用DDR的方式,那么数据的带宽和时钟带宽是相同的,这样对设计更友好,可以使用相同的IO管脚。

从图1.4可以看出,当使用DDR传输时,时钟和数据的变化速率是相同的,这意味这最大带宽是相同的,基带信号满足 数据速率 = 2*B,B表示带宽。

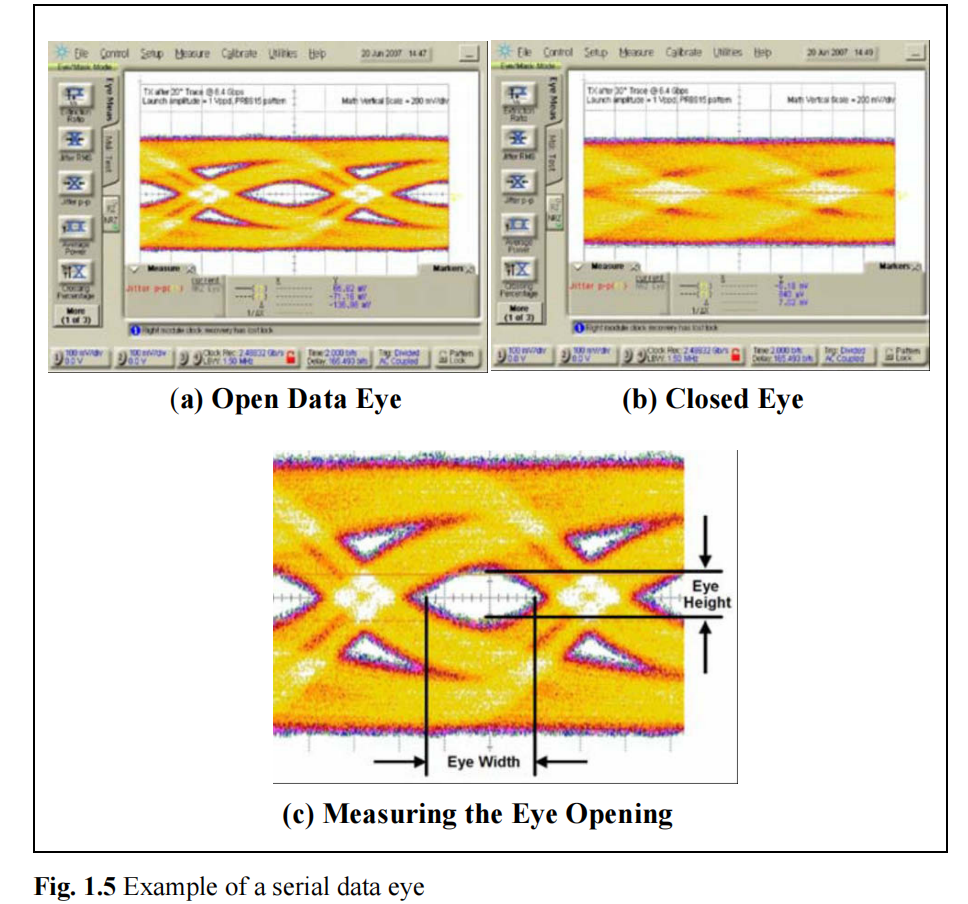

那么如何评价信号质量?如何采样能够得到正确的数据?可以看下面的眼图。

图中的线条越分明说明信号质量越好,我们可以在眼的横坐标中心采样,这个时刻是一个码元的波峰或者波谷,在判定码元为0或者1时最为准确。信号的上升和下降时间约小,眼图质量越好,信号的转换速率越大眼图质量越低,同时工艺,电压,温度都会影响眼图的质量。如果上升时间和下降时间的比例差别越大,眼图质量也会变差(说明码间串扰比较大)。

为了提高信号质量,可以将单端信号替换为差分信号,可以减小共模干扰,这种对称的数据也可以避免下降时间和上升时间不一致导致的眼图闭合的问题。虽然差分信号会使用两倍的IO管脚,但是可以带来更好的抗噪声表现,数据速率能够提高数倍。

图1.3中的接口时钟与用于发送(launch)数据的时钟相同,通常从时钟分布网络中尽可能靠近实际发送数据的触发器(flip-flops)的位置驱动。任何不属于数据路径和时钟路径共用部分的电路都会引入相位变化。硅工艺变量在同一芯片上的不同电路之间存在差异,电源分布网络可能对不同电路产生不均等的电压降(可能因开关电流而变化),芯片上不同位置的温度也可能不同。在计算延迟、建立时间(setup times)和保持时间(hold times)以确保正确捕获接收数据时,必须考虑所有这些参数的容差和限制。在更高的比特/波特率下,这些参数可能会显著缩小眼图开度(eye opening),并成为限制接口速度的主要因素。

为了最大化眼图宽度,时钟树(clock tree)到每个数据触发器和时钟输出的路径应尽可能共享更多电路,时钟的输出驱动器应与数据的输出驱动器相似。理想情况下,同一个时钟缓冲器应驱动所有数据触发器的时钟输入。数据总线的位数越多,这种实现就越困难。I/O驱动器必须根据封装引脚连接的布局规则(groundrules)进行物理分布。电路之间的距离越大,工艺、电压和温度变化越大,时钟分布网络中因距离原因无法共享的电路就越多。

总而言之,时钟和数据最好是要使用完全相同的路径,采用完全相同的IO管脚,数据传递最好是使用差分信号。

我们也可以采用下面这种结构:

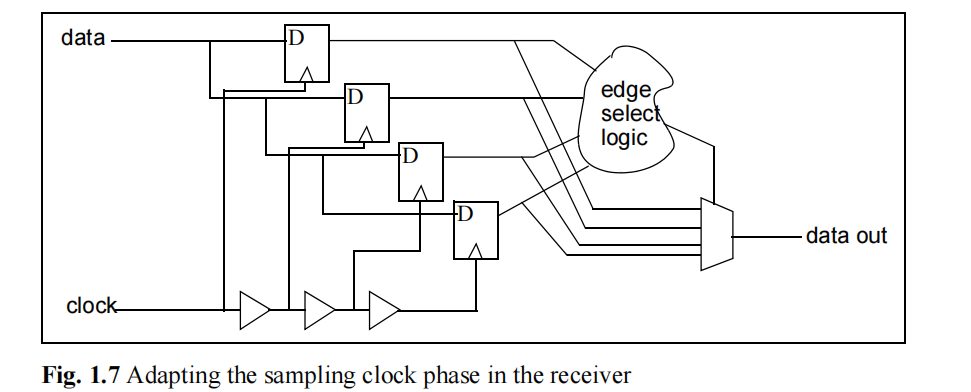

在图1.7中,data的每一个bit位都可以采用独立的时钟来采样,因为data的每个bit位的数据相位可能不一样,因此使用完全相同的clk很难保证正确采样所有bit位,那么可以通过控制抽头延迟,即图中的三角形Buffer。但是这种方式需要提前训练出每个bit位的最佳采样时间,速率可以提高到几Gbps。

但是正如上面所说,时钟和数据最好是要使用完全相同的路径,采用完全相同的IO管脚,数据传递最好是使用差分信号。

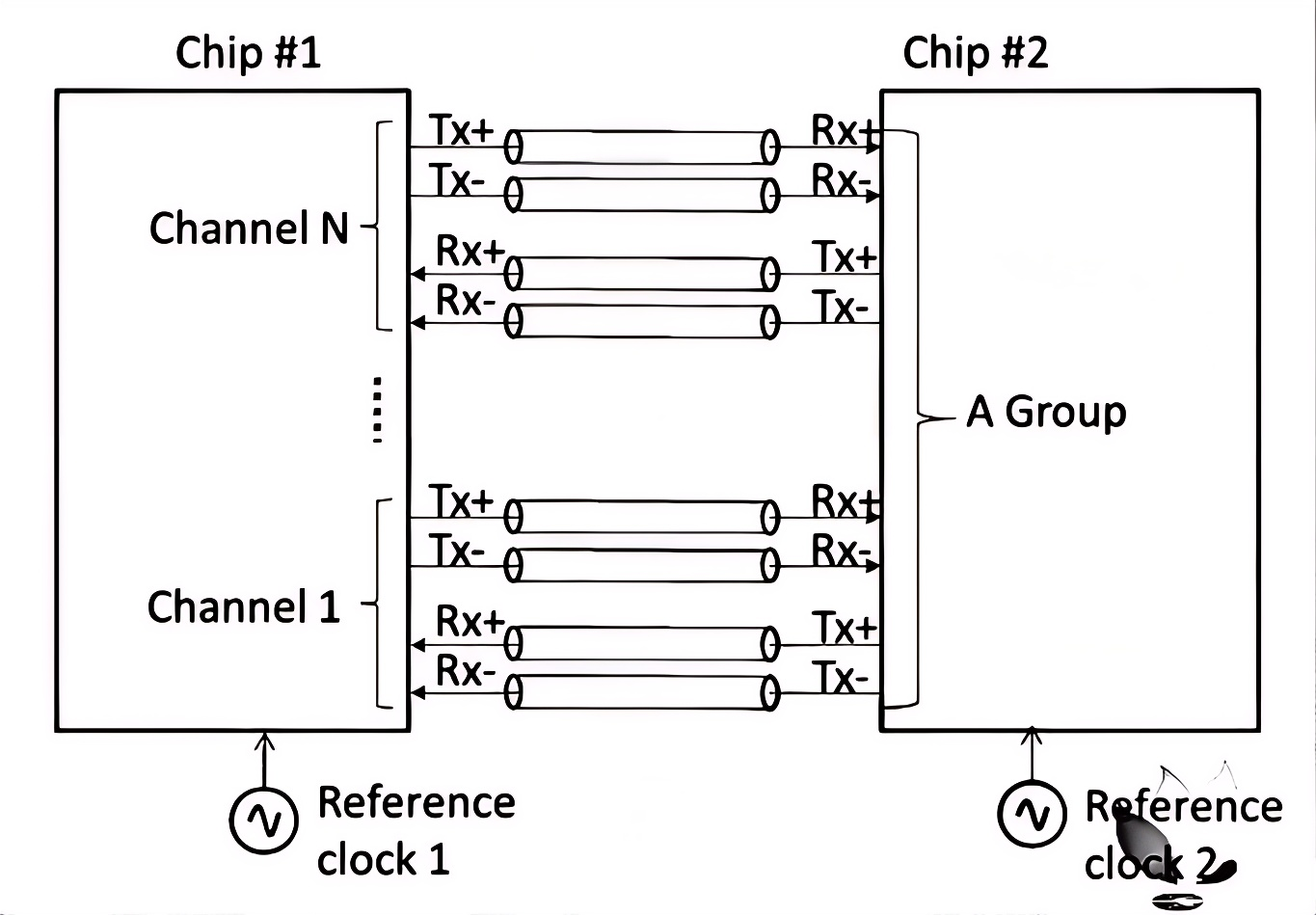

那么我们直接去掉时钟信号,只用2个IO用于传递差分信号,在接收端通过差分信号恢复出时钟并进行采样就能达到最佳性能,这也就是serdes的雏形,

评论